北京联盛德微电子有限责任公司

# W520M 芯片规格书

V1.0.0

北京联盛德微电子有限责任公司 (WinnerMicro)

地址：北京市海淀区阜成路 67 号银都大厦 18 层

电话：+86-10-62161900

公司网址：[www.winnermicro.com](http://www.winnermicro.com)

北京联盛德微电子有限责任公司

## 文档历史

## 目录

|                    |   |

|--------------------|---|

| 1 产品简介 .....       | 2 |

| 2 产品特性 .....       | 2 |

| 2.1 Wi-Fi 特性 ..... | 2 |

| 2.2 音频特性 .....     | 4 |

| 3 封装规格及管脚定义 .....  | 4 |

| 4 电特性 .....        | 7 |

| 5 封装信息 .....       | 7 |

## 1 产品简介

本产品是一颗嵌入式 Wi-Fi 音频编解码 SoC 芯片。芯片内置 32 位 ARM 处理器，支持 IEEE802.11b/g/n 国际通讯标准。集成 MP2、MP3、WMA、WAV、FLAC(16/24bit)、AAC 解码器；支持 WAV、MP2、MP3 编码器。内置 BBP/MAC/LNA/PA/Switch。支持 2Mbps UART、SPI、GPIO、I<sup>2</sup>C、PWM、ADC 等接口。支持 2 次开发 SDK 平台，支持远场语音唤醒，支持微信/OneShot 一键配网；自然语音交互、远程互聊等功能。该芯片大小为 10mmX10mm， QFN 88PIN 封装。适用于云故事机、AI 机器人、智能音箱等产品应用。

## 2 产品特性

### 2.1 Wi-Fi 特性

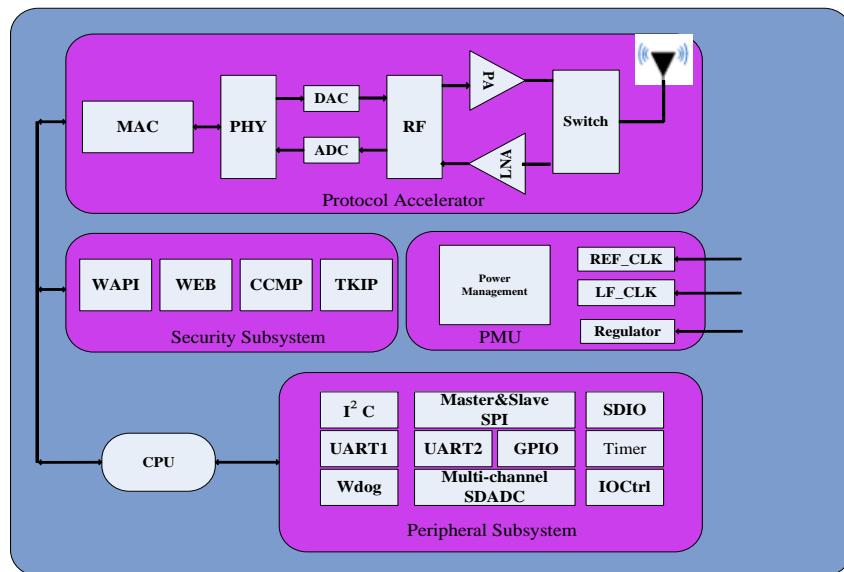

嵌入式 Wi-Fi 内部框图

- ◆ 支持 IEEE802.11b/g/i/e/n/WAPI

- ◆ 集成 MAC、BB、RF、PA、ADC、DAC 本振泄漏校准电路、射频开关

- ◆ 最大发射功率典型值：

- 11b:  $16 \pm 1\text{dBm}$

- 11g:  $14 \pm 1\text{dBm}$

- 11n:  $14 \pm 1\text{dBm}$

- ◆ 接收灵敏度典型值：

- 11b: -91dBm

- 11g: -85dBm

- 11n: -85dBm

- ◆ 超低功耗设计：支持动态功耗管理，芯片工作分为 Work、Light Sleep、Deep Sleep、Standby

四种工作模式。

◆ 集成：

- 1) ARM9 RISC 处理器 (ARM946E-S 处理器, 8K ICache, 8K DCache, 主频 160MHz) ;

- 2) 384BK 片上指令 RAM;

- 3) ROM、EFUSE, 其中 ROM 用来存放 CPU 上电后的初始化固件, 主要完成工作固件的加载, 芯片寄存器空间的初始配置等工作。EFUSE 用来存放芯片特征信息, 包括 MAC 地址, 物理层参数、厂商 ID 等;

- 4) ISRAM (指令 SRAM, 存储 CPU 运行需要的指令) ;

- 5) DSRAM (可用于存放指令或发送/接收数据) ;

- 6) DMA 模块 (实现数据在 SRAM 内、慢速设备之间、SRAM 与慢速设备之间的数据搬移; ) ;

◆ 网络模式：

- 支持 BSS 网络 AP 工作模式;

- 支持 BSS 网络 STA 工作模式;

- 支持 BSS 网络总数为五个的 STA 和 AP 同时工作模式;

- 支持 IBSS 网络

◆ 接入容量：

- BSS 网络作为 AP 使用时, 加密时支持站点与组播的总和为 32 个;

- IBSS 网络中加密时支持 16 个站点 (以上站点数不包括本地站点) ;

- ◆ 支持多种节能机制：支持 802.11e U-APSD 节能机制； WiFi WMM-PS 节能机制； BSS 中的 PS-POLL 节能机制；

- ◆ 支持低成本的 40MHz 晶体

- ◆ 安全性：支持 WEP64、WEP128 加密，支持 CCMP、TKIP、wapi2.0

- ◆ 网络共存：支持 B/G/N 保护，支持 20M/40M 共存，支持的信道保护方式为：RTS/CTS 保护，CTS-to-self 保护；

- ◆ 快速便利的测试方案：通过测试寄存器即可检查芯片状态

## 2.2 音频特性

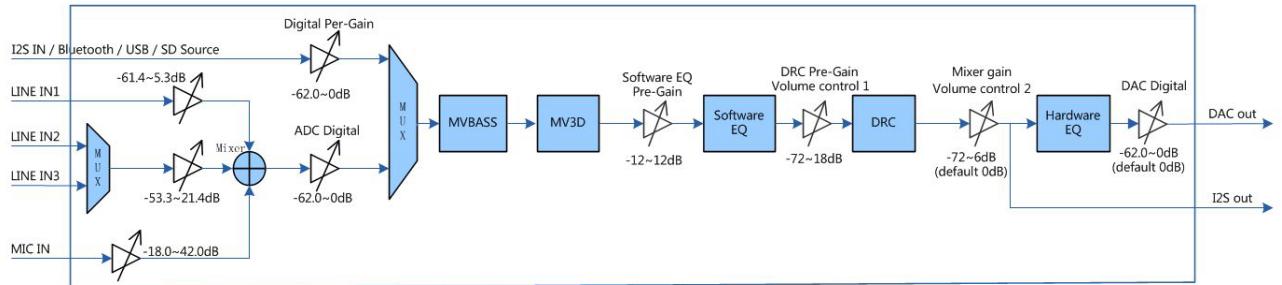

编解码内部框图

- ◆ MP3、WMA、WAV、FLAC (16/24bit)、AAC 解码器

- ◆ WAV、MP2、MP3 编码器

- ◆ 高品质 20-bit DAC

- ◆ 丰富的音效处理：MVBASS、MV3D、MVEQ

## 3 封装规格及管脚定义

该芯片采用 QFN88 封装，表 3.1 给出了 QFN88 封装的管脚定义

表 3.1 QFN88 封装管脚定义

| 管脚编号 | 管脚名称         | 管脚特性 | 说明                      |

|------|--------------|------|-------------------------|

| 1    | LDO_DPLL_OUT | P    | DPLL 的 LDO 输出电源, 1.2V   |

| 2    | VDD_DIG      | P    | 数字输入电源, 3.3V            |

| 3    | XTAL_IN      | I    | 40MHz 晶体输入端             |

| 4    | XTAL_OUT     | O    | 40MHz 晶体输出端             |

| 5    | VSS_DLDO     | G    | 数字 LDO 地                |

| 6    | DLDO_IN      | P    | 数字 LDO 输入电源, 1.5V       |

| 7    | VDD_ISO1     | P    | 数字和模拟电源域之间的电源隔离管脚, 3.3V |

| 8    | VSS_ADDA_D   | G    | AD/DA 数字地               |

| 9    | VDD_ADDA_D   | P    | LDO 输出 AD/DA 数字电源, 1.2V |

| 10   | ALDO_IN3     | P    | 模拟 LDO 输入电源, 1.5V       |

| 11   | VDD2P8_DA    | P    | LDO 输出 DA 电源, 2.8V      |

| 12   | VDD3P3_DA    | P    | DA 输入电源, 3.3V           |

| 13   | VDD_ADDA_A   | P    | LDO 输出 AD/DA 电源, 1.2V   |

| 14   | BGR_REX      | AI0  | 外接一个阻值为 24KΩ 的下拉电阻到地    |

| 15   | VDD3P3_BGR   | P    | BandGap 输入电源, 3.3V      |

| 16   | VDD_PRE      | P    | LDO 输出预分频器电源, 1.2V      |

|    |             |                     |                          |

|----|-------------|---------------------|--------------------------|

| 17 | VDD_CP      | P                   | LDO 输出电荷泵电源, 1.2V        |

| 18 | VSS_CP      | G                   | 电荷泵地                     |

| 19 | VDD_VCO     | P                   | LDO 输出 VCO 电源, 1.2V      |

| 20 | ALDO_IN2    | P                   | 模拟 LDO 输入电源, 1.5V        |

| 21 | VDD_LO      | P                   | LDO 输出本振缓冲器电源, 1.2V      |

| 22 | VDD_DMIF    | P                   | LDO 输出下变频及中频接收部分电源, 1.2V |

| 23 | ALDO_IN1    | P                   | 模拟 LDO 输入电源, 1.5V        |

| 24 | VDD_LNA     | P                   | LDO 输出 LNA 电源, 1.2V      |

| 25 | RF_INN      | AI                  | 射频接收信号输入端                |

| 26 | RF_INP      | AI                  | 射频接收信号输入端                |

| 27 | VDD3P3_TRSW | P                   | 射频收发开关输入电源, 3.3V         |

| 28 | ANTP        | <td>射频信号输入/输出端</td> | 射频信号输入/输出端               |

| 29 | ANTN        | <td>射频信号输入/输出端</td> | 射频信号输入/输出端               |

| 30 | GP_C13      | IO                  | SWCLK                    |

| 31 | GP_C14      | IO                  | SWD                      |

| 32 | VDD3P3_PA2  | P                   | PA 输入电源, 3.3V            |

| 33 | VSSA        | G                   | 模拟地                      |

| 34 | PAD_VMID    | AI                  | 内部参考电压                   |

| 35 | PAD_DACR    | AO                  | 音频右声道输出                  |

| 36 | PAD_DACL    | AO                  | 音频左声道输出                  |

| 37 | VDDA        | P                   | 模拟电源输入, 3.3V             |

| 38 | XTAL32_IN   | I                   | 32.768KHz 晶体输入端          |

| 39 | XTAL32_OUT  | O                   | 32.768KHz 晶体输出端          |

| 40 | CVDD_PMU    | P                   | PMU 输入电源, 1.2V           |

| 41 | PAD_MIC     | AI                  | MIC 输入                   |

| 42 | PAD_VCOM    | AI                  | MIC 参考电压                 |

| 43 | RST_N       | I                   | 芯片全局复位信号, 低有效            |

| 44 | BOD_DET     | AI                  | BOD 检测电压, 接 3.3V 电源      |

| 45 | LDO_BB1_IN  | P                   | 数字 LDO 输入电源, 1.5V        |

| 46 | PAD_XO_RLOC | O                   | 32.768KHz 晶体输出端          |

| 47 | PAD_XI_RLOC | I                   | 32.768KHz 晶体输入端          |

| 48 | LDO_OUT33   | P                   | LDO 输出, 3.3V             |

| 49 | LDO_VIN     | P                   | LDO 输入电源, 5V             |

| 50 | LDO_OUT12   | P                   | LDO 输出, 1.2V             |

| 51 | VDD12_DCO   | P                   | RTC 电源, 1.2V             |

| 52 | PVDD33_1    | P                   | WLAN 电源域输入电源, 3.3V       |

|    |                               |    |                                  |

|----|-------------------------------|----|----------------------------------|

| 53 | H_SPI_INT<br>/UART1_RXD/GPIO7 | I  | H-SPI_INT, (UART1) RXD,<br>GPIO7 |

| 54 | H_SPI_CS/GPIO3                | IO | H-SPI_CS, GPIO3                  |

| 55 | H_SPI_DI/GPIO4                | IO | H-SPI_DI, GPIO4                  |

| 56 | H_SPI_DO/GPIO5                | IO | H-SPI_DO, GPIO5                  |

| 57 | UART1_TXD/GPIO6               | IO | UART1_TXD, GPIO6                 |

| 58 | GPIO11                        | IO | GPIO11                           |

| 59 | GPIO12                        | IO | GPIO12                           |

| 60 | GPIO13                        | IO | GPIO13                           |

| 61 | GP_A10                        | IO | GPIO_A10                         |

| 62 | GP_A13                        | IO | SPI_HOLD, GPIO_A13               |

| 63 | GP_A14                        | IO | SPI_CLK, GPIO_A14                |

| 64 | GP_A15                        | IO | SPI_MOSI, GPIO_A15               |

| 65 | GP_A16                        | IO | SPI_WP, GPIO_A16                 |

| 66 | PVDD33_2                      | P  | WLAN 电源域输入电源, 3.3V               |

| 67 | GP_A17                        | IO | SPI_MIDO, GPIO_A17               |

| 68 | GP_A18                        | IO | SPI_CS, GPIO_A18                 |

| 69 | GP_A19                        | IO | GPIO_A19                         |

| 70 | GP_A20                        | IO | GPIO_A20                         |

| 71 | GP_A21                        | IO | GPIO_A21                         |

| 72 | GP_A24                        | IO | GPIO_A24/BUART_RX                |

| 73 | GP_A25                        | IO | GPIO_A25/BUART_TX                |

| 74 | LS_SPI_CLK/GPIO10             | IO | LS-SPI_CK, GPIO10                |

| 75 | UART0_RXD/GPIO14              | IO | UART0 的 TXD 信号, GPIO14           |

| 76 | UART0_RXD/GPIO15              | IO | UART0 的 RXD 信号, GPIO15           |

| 77 | LS_SPI_CS/GPIO18              | IO | LS-SPI_CS, GPIO18                |

| 78 | LS_SPI_DI/GPIO19              | IO | LS-SPI_DI, GPIO19                |

| 79 | LS_SPI_DO/GPIO20              | IO | LS-SPI_DO, GPIO20                |

| 80 | VSS                           | G  | 数字地                              |

| 81 | LDO_BB3_OUT                   | P  | 数字 LDO 输出电源, 1.2V                |

| 82 | LDO_BB3_IN                    | P  | 数字 LDO 输入电源, 1.5V                |

| 83 | LDO_DPLL_IN                   | P  | DPLL 的 LDO 输入电源, 1.5V            |

| 84 | TX_EN                         | O  | RF 发射状态指示信号, 高有效                 |

| 85 | RX_EN                         | O  | RF 接收状态指示信号, 高有效                 |

| 86 | SDADC_AIN1                    | A  | SDADC 模拟输入端口 1                   |

| 87 | SDADC_AIN0                    | A  | SDADC 模拟输入端口 0                   |

| 88 | VDD33_SDADC                   | P  | SDADC 输入电源, 3.3V                 |

## 4 电特性

芯片电源及 I/O 电压参数(27 环境下):

表 4.1 直流电气特性

| 参数      |       | 最小值  | 典型值 | 最大值  | 单位 |

|---------|-------|------|-----|------|----|

| 3.3V 电源 | 供电电源  | 3.0  | 3.3 | 3.6  | V  |

| 1.5V 电源 | 供电电源  | 1.35 | 1.5 | 1.65 | V  |

| 1.2V 电源 | 供电电源  | 1.08 | 1.2 | 1.32 | V  |

| II      | 输入漏电流 | -1   |     | 1    | uA |

| VIL     | 输入低电压 | -0.3 |     | 0.8  | V  |

| VIH     | 输入高电平 | 2    |     | 3.6  | V  |

| VOL     | 输出低电平 | -    |     | 0.4  | V  |

| VOH     | 输出高电平 | 2.4  |     | -    | V  |

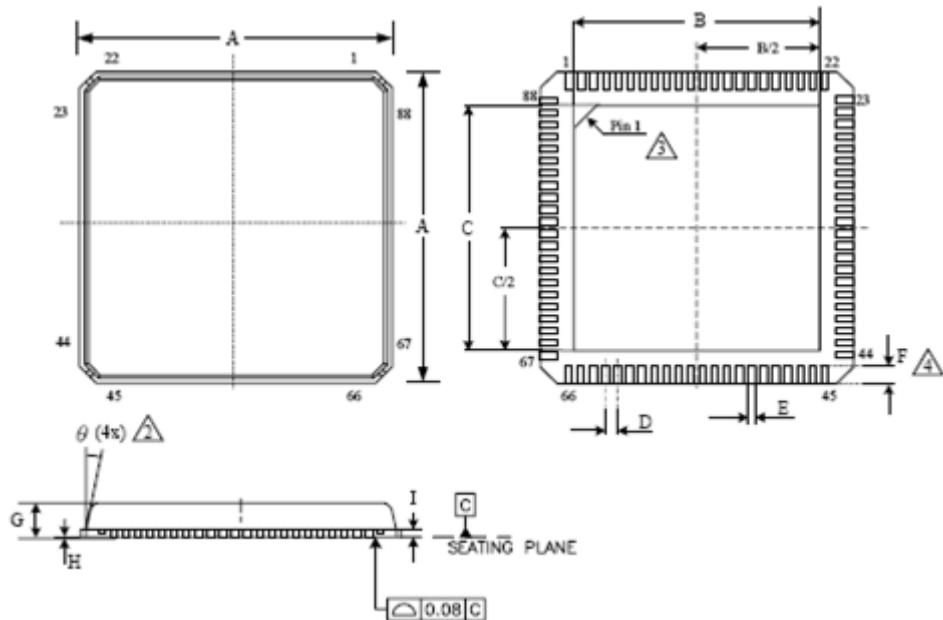

## 5 封装信息

图 5.1 和表 5.1 中给出了 QFN88 封装的相关参数

图 5.1 QFN88 封装参数

表 5.1 QFN88 封装参数表

| No. of Leads | SYMBOL |   |   |   |   |   |   |   |    |

|--------------|--------|---|---|---|---|---|---|---|----|

| 88(10x10)    | A      | B | C | D | E | F | G | H | II |

## 北京联盛德微电子有限责任公司

|              |     |    |      |      |     |      |      |     |      |       |

|--------------|-----|----|------|------|-----|------|------|-----|------|-------|

| Milli-meters | MIN | 10 | 6.60 | 6.60 | 0.4 | 0.15 | 0.35 | 0.7 | 0    | 0.203 |

|              | MAX |    | 8.25 | 8.25 |     | 0.25 | 0.60 | 0.9 | 0.05 |       |